前言

计组是我听过的最脑阔疼的课。不过已经考过了orz以及,大家学的计组内容可能不一样,这篇复习包括的内容应该是比较简略的。

数据信息表示

(设机器字长8位)原码:正数符号位0,负数符号位1,其他7位按一般方法表示数的绝对值。

补码:用0到M区间的数表示,x的补码=(M+x)mod M。如果连同符号位放在数轴上,可以看出正数用前半部分数轴表示(00000001到01111111即2的7次方-1),负数用后半部分数轴表示(10000000到11111111即2的8次方-1),0用00000000表示,也可以看出来负数比正数多表示一个数字。补码可以用原码推出,其正数与原码一致,负数则保留原码符号位,剩下7位全部取反再加1;也可以保留原码符号位,从低位开始的第一个1保留,比第一个1高的位取反(两种方法其实一样)。

反码:正数的原码、反码、补码相同。负数可由原码保留符号位,其余7位取反得到。反码中00000000与11111111都表示0。

移码:移码的符号位与前面三种机器码相反,形式上与补码除符号位没有差异。从数轴上来看,它的前半段就是补码的后半段,后半段也是补码的前半段,因此0的表示是10000000。

浮点数(N=M*R^E):从高位到低位一般是符号位、阶码E(整数)、尾数M(小数)

IEEE 754标准:(单精度格式下)该标准中,N=M*2^E,符号位占1位,阶码E用移码表示(E占8位,表示范围-126~127),尾数M用原码表示,但尾数隐含最高位为1,原码表示1以后的部分,用23位表示了24位的信息。

汉字的表示:外码即输入码,机内码(内码)是汉字的基本编码,GB、GBK、BIG5、UNICODE都是汉字机内码。

校验码:奇校验和偶校验:在原有n位码后加一位校验位,使得n+1位码中1的个数为奇数/偶数。

数值运算及运算器

加减运算:补码加法可以直接相加,补码减法通过取减数相反数的补码转换为补码加法。参加运算的数符号相同,结果的符号位不同时则溢出,也可以根据符号位和最高有效位的进位判断,或用变形补码。

乘法、除法:原码一位乘和不恢复余数法,虽然做过题还是非常麻烦。

浮点运算:对阶(阶码较大的数M右移,大阶对小阶)、尾数求和/相乘、规格化

存储系统

RAM(Random Access Memory):随机存取存储器,用作主存和高速缓冲存储器。

ROM(Read Only Memory):只读存储器,即使断电也不会丢失数据

SAM(Sequential Access Memory):顺序存取存储器,只能按某种顺序存取,数据存取时间与介质上的物理位置有关,典型如磁带。

DAM(Direct Access Memory):直接存取存储器,介于RAM和SAM之间,存取数据时DAM直接指向一块区域,在这块区域中顺序查找或等待,也是磁盘的工作方式。DAM和SAM对数据的存取都与位置有关系,统称串行访问存储器。

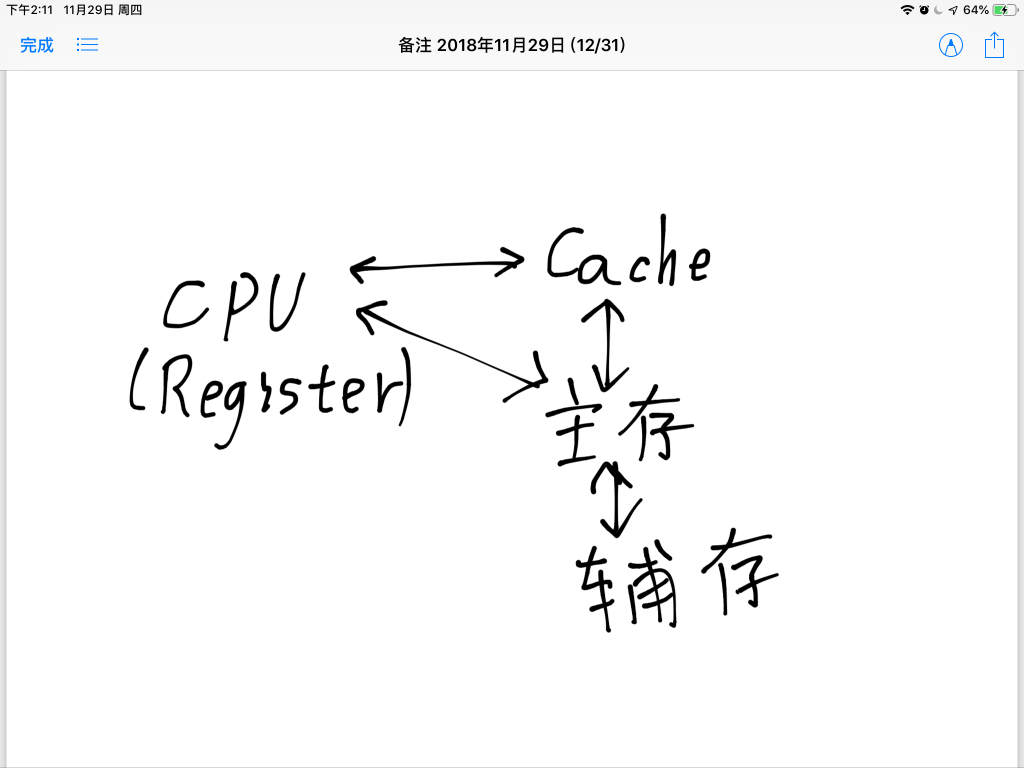

计算机存储结构:

随机存取存储器和只读存储器:现在多为MOS(金属-氧化物-半导体)型半导体电路,RAM分为StaticRAM和DynamicRAM,前者用于寄存器(Register)和Cache,后者用于主存。SRAM芯片的一部分地址线选择存储矩阵中的行,另一部分地址线选择列,地址线可能接多位,如每条列线接4位,共4条列线,可对64列地址选择,芯片有片选端CS(低电平选择)和写使能控制端WE共同控制芯片状态。

8086寄存器与寻址方式

汇编

更多章节

由于已经考过了,不整理了,下面?是笔记:

第七章 输入输出系统及外围设备

主机: cpu——–总线

ram rom 接口 接口

硬盘 外设

硬件接口传输的信息包括:地址、数据、命令、状态

端口:接口中能被cpu读写的寄存器R,一般有数据端口(数据缓冲寄存器)、命令端口(命令寄存器)、状态端口(状态寄存器,供CPU读取)

输入/输出接口分类:

1.按(接口到外设的)数据传送方式:串行、并行

2.按CPU访问外设的控制方式

3.按是否需要统一的控制时钟:同步、异步

4.按通用性:通用、专用

输入输出设备的编址:

1.独立编址:有重复,两套指令,内存容量=2^n,微机系统、单片机、嵌入式设备采用

2.统一编址:端口一般在高地址,内存容量小于2^n(地址线的数目)

主机与外设间信息传输的控制方式:

一、程序直接控制方式

1.立即程序传送方式:一般用于led、数码管、开关,需要设备时刻准备好,无需查询状态

2.程序查询方式:1⃣️cpu(一直)查询外设状态 2⃣️外设准备好传输数据 特点:成本低,适用广,硬件简单,CPU利用率低,实时性差

二、程序中断方式

中断:

按中断源分为外部中断(外设和机器故障引起,分为可屏蔽,一般I/O有数据请求,属正常事件,由CPU的INTR引脚发出,和不可屏蔽,一般预示机器故障由CPU的NMI引脚发出,不受IF控制,如低压中断,内存错误中断)和内部中断(由CPU内部引起的中断,如溢出中断,除数为0,软件调试单步中断,软件中断:INT中断)

ISR入口地址形成方式:向量中断。256个中断源入口地址处于内存最低处,占用000H到3FFH(1K)。内部中断优先级最高,其次不可屏蔽中断(NMI),可屏蔽的外部中断(INTR),单步中断,普通软件

中断的嵌套:高打断低优先级

CPU中断过程:中断请求,中断判优,保护断点,转入InterruptServiceRoutine,中断返回

特点:外设主动,CPU利用率高,CPU外设并行工作,实时性好

应用:大多数设备

三、DirectMemoryAccess直接存储器存取方式

需要DMAController(硬件复杂),不需要CPU控制受DMAC控制,以硬件速度传输(只取决于硬件延时),速度快,一次传输一批数据,代价较高

DMA请求后CPU响应DMA信号,DMA控制总线和传输,DMA结束发送给CPU

四、通道控制IOP传输方式(大型机、巨型机使用)

通道是一种专门处理I/O请求的控制器,一次传输一个文件(数据量更大),代价更高,传输过程不需要CPU干预,整批文件传输完成向CPU报告中断

第四章 指令系统

控制信息:指令(程序) I

数据信息:操作数

指令系统:支持的指令的集合,分为CISC、RISC,不同cpu一般不兼容,x86兼容

指令格式:操作码(OP) 地址码(操作数、OD)

设计指令系统:

1.指令字长度:操作码和地址码的位数,一般不等长,和机器字长有一半、两倍、四倍的长度关系,新式RISC系统长度一般和机器字长一样

2.操作码结构:分为等长(n位支持2^n种指令)和可变长(所有指令需要唯一的操作码)

3.地址码设计:

分为四地址指令(操作码+4个操作数:A1和A2运算,结果存放到A3,A4为下一条指令地址,地址过多,现代计算机一般不采用,而使用pc寄存器,操作后自动+1,指向下一条地址)、

三地址指令(x86支持,RISC主要采用三地址指令,比四地址指令少了第四个操作数,8086不支持)、

两地址指令((A1)OP(A2)➡️A2,是x86计算机的主流指令)、

单地址指令(x86支持,常用,OP(A)➡️A,可以为双操作数指令(AX)OP(A)➡️AX,另一操作数隐含,可能位于累加寄存器AX)、零操作数指令(x86支持,常用,空指令操作、停机指令等,或是有操作数的堆栈指令,对固定的操作数如堆顶、标志R、累加R)

缩短指令的长度:4➡️3,增加pc寄存器。3➡️2,把其中一个设为目标寄存器。2➡️1,隐含寄存器R。也可以使用多种内存寻址,缩短内存od位数

操作数:一般有立即数10,200、寄存器R:AX,BX(使用二进制编号)、内存单元:需要地址、固定位置:标志R、累加R、栈顶

补充:机器字长,操作字长度,寄存器宽度,计算器位数,总线根数 8086-16位 386-32位

低级语言:机器语言(二进制,CPU直接识别,可执行文件的内容,如10010001)、汇编语言(又叫符号语言,使用助记符替代操作码,命名寄存器R,变量名替代内存单元地址,汇编即将源码翻译成机器指令,反汇编即反过程)

三、寻址方式:寻找(下一条)指令和操作数地址

1.指令寻址方式:分为顺序寻址方式(大多数指令)和跳转寻址方式(少量指令,取指令后pc也会递增,执行阶段修改pc值而跳转,如条件跳转、无条件跳转、子程序调用、子程序返回、中断调用、中断返回、循环指令)

2.数据寻址方式:隐含寻址(对隐含位置做操作,AX隐含寄存器,FLAG标志寄存器,栈顶)、立即寻址(立即数寻址,指令的地址码部分是操作数本身,如ADD AX,100)、寄存器R寻址(地址码字段给出寄存器编号,如ADD AX,BX)、直接寻址(指令直接给出操作数在内存中的地址)、内存间接寻址(指针的原理,地址码部分给出存放操作数地址存储单元的地址,需要读两次,速度太慢)、R间接(用编号读取地址,再读取操作数)、变址寻址和基址寻址(1ADD+1访问内存M,后者一般用于内存重定位,仅改变偏移)、相对寻址(特指PC与地址码给的偏移相加,一般用在跳跃式寻址)、堆栈寻址(操作数地址由栈顶指针SP指定)

四、8086寻址方式示例

汇编语言知识要求:CPU结构4、寻址方式4、指令系统4、伪指令8、编程技巧和程序结构9-13

8086CPU分为执行部件EU、总线接口单元BIU,R16位长,DB16根,ALU16位,地址总线AB20根,因此最多支持1M内存

读取M的物理地址长20位,逻辑地址(汇编指令的地址)由段地址(16位的物理地址首地址,分为CS,DS,ES,SS)和偏移地址(16位,可能是立即数,R(BX,SP,BP,SI,DI))组成,cpu会转换逻辑地址为物理地址(段地址左移4位+偏移地址)

4个段地址寄存器,作为当前使用的段:

CS(代码段R):存放汇编指令(程序)。不允许被MOV修改

DS(数据段R):存放常规数据或乘数

SS(堆栈段R):一个栈,存放数据

ES(附加段R):字符串指令中用到的数据,很少用到

8个16位通用寄存器,可存放普通数据:

4个16位R:AX(累加器),BX(基址R),CX(移位或循环次数,计数R),DX(数据R,可以和AX(L)合起来作为32位存储器)

8个8位R:AH(高字节,高8位),AL(低字节),BH,BL,CH,CL,DH,DL

地址指针R:

IP(即pc,指令指针寄存器),cpu从CS:IP处取指令

标志寄存器FlagsRegister(存储PSW,16位长,)

状态位6个:CF(0)进,借位标志、PF、AF(为1表示)、ZF、SF、OF(11,为1表示前一步溢出)

控制标志位3个:

主存特点:字寻址,高地址在高8位字节,低地址低8位字节

指令 CS:IP

堆栈 SS:SP SS:BP

数据 DS:偏移 ES:偏移 SI DI BX可以作为数据寄存器

8086支持的寻址方式:

1.寄存器寻址:指令给出寄存器地址 mov AX,BX(BX传给AX)

2.立即(数)寻址:只支持8/16位,只能出现在原操作数中,不能出现在目的操作数中

3.直接寻址:

如mov AX,VAR或 mov AX,[VAR]

MOV AX,DS:[1200H]或省去DS(默认)

4.R间接寻址 mov AX,[BX] SI,DI之一

4.变址寻址:只给出位移量

5.基址变址寻址:基址寄存器(BX-r默认ds或BP-r隐含ss) 变址寄存器(SI或DI) 偏移量 相加

6.与转移地址相关的寻址方式:段内直接寻址

[VAR]是间接寻址,[200H]是直接寻址

五、8086指令类型

1.数据传输指令:两个操作数长度一致,2地址不能都是

2.算术运算指令3.逻辑运算指令4.程序控制

指令系统:指令的格式、功能、限制

关于mov指令,不能向cs传递,段寄存器不能互相存储

字变量16位 字节8位

六、8086/8088指令

MOV

XCHG(exchange):不能使用段R、立即数

PUSH、POP:只能是宽度16位的R或内存单元

(用的不多)XLAT:查表,BX指向表格首地址,AL决定第n项

标志寄存器操作LAHF,将标志R低八位传送到AH;SAHF相反

地址传送指令 LEA(LoadedEffectiveAddress) DST,SRC,将源OP在数据段中的偏移地址传送给DST 例:lea si,buf。Mov bx,[si]

(用的不多)LDS/LES DST(16位通用寄存器),SRC(内存单元):2字节偏移地址DST,2字节段地址DS/ES

算术运算指令 ADD DST,SRC;不能同时是内存单元,宽度一致,2寄存器、寄存器+内存单元、寄存器+立即数

ADC 带进位加法

INC DST;操作数+1,DST只能是通用寄存器和内存单元

减法SUB DST,SRC; DST-SRC➡️DST

SBB带借位减法,用于扩展减法

DEC DST;和INC相反

NEG求负数(求补)

比较指令 CMP DST,SRC; DST-SRC并设置标志位,DST和SRC内容不受影响

乘法指令

无符号数乘法MUL SRC(不能立即数,可以内存单元或R);另一操作数载AL或AX中,8位时取AL,结果保存在AX;16位时与AX相乘,高16位DX,低16位AX

带符号数乘法指令IMUL

无符号数除法DIV SRC;和乘法相似,字节除法:AX/SRC➡️AL,余数➡️AH;字除法:(DX:AX)/(SRC)➡️AX,余数➡️DX

IDIV

类型转换指令 指令格式:CBW/CWD(符号位扩展);隐含使用AH/DX;CBW:AL向AH扩展(用符号位填充)CWD:用AX符号位向DX扩展

逻辑运算指令 AND/OR/XOR DST,SRC;要求宽度一致,DST不能是立即数,两个不能同时是内存单元 NOT DST;

异或 XOR AX,AX 清零

测试指令:TEST DST,SRC;按位与,设置标志位但不传结果给DST

COMPARE比较大小和正负,

移位指令:算术左移/右移 SAL/SAR DST,COUNT(最高位到CF,最低位补0;最低位到CF,最高位补符号位)

逻辑移位:SHL/SHR DST,COUNT 最高位也补0

循环移位:ROL/ROR DST,COUNT

带进位循环左移/右移:RCL/RCR DST,COUNT,带上CF,循环移位 COUNT=1时可用1,COUNT!=1时用CL替代

传送类指令一般不影响标志位,算术和逻辑运算一般设置标志位

无条件转移指令:JMP 目标地址;

条件转移指令:JXXX 目标地址;

JCXZ 目标地址,测试CX地址,CX=0,跳转

循环控制指令LOOP 目标地址;CX-1,CX不为0则循环,CX为0则顺序执行

子程序调用与返回 CALL 目标地址 影响堆栈

RET[PARA] 影响堆栈

中断调用与返回

INT n(调用n号中断功能)

IRET 在中断服务程序的最后,无参数,从堆栈弹出原有地址

NOP延时 HLT停机 WAIT等待

七、CISC与RISC

Complex Instruction Set Computer

执行一条指令要多次访问主存,需多个微周期,寻址方式复杂,流水线中长指令执行妨碍其他指令

Reduced Instruction Set Computer

ARM、DSP、RAMIP、MSP、AVR

第八章

汇编:不区分大小写,注释加;,一个程序由若干个段组成

DATA SEGMENT

A DB 25;DB型即8位字节变量

Y DB ?;

DATA ENDS

COSEG SEGMENT 伪指令

ASSUME CS:COSEG,DS:DATA,SS:STACK1 伪指令,把DS指向数据段首地址

START:(程序入口地址)

MOV Y,A;

COSEG ENDS

汇编语句种类

指令语句:cpu执行二进制代码

位指令语句/命令语句:汇编程序的指示

宏指令语句:用户自定义的指令

?宏和子程序

格式:名字+操作符+操作数+;+注释

指令:[标号:]助记符[操作数[,操作数]][;注释]

伪指令:[名字]定义符[参数,…][;注释]

命名规则:可以用?@_$数字和英文,第一个字符不能时数字,前31字符有效,不允许用保留字(指令、伪指令、寄存器)

伪指令:

EQU:符号 equ 表达式,如const equ 10 后面不能再重新定义

=:cont=5 后面可以改变

变量名 db/dw/dd 表达式1,2。。 用于分配空间 db 1byte; dw word 2; dd dword 4;dq qword 8;dt 10byte 前面的字节在高位,一般放在数据段或附加段,不能放代码段;变量拥有段属性(属于哪个段),偏移属性,类型属性

字符/字符串 一般用db声明 变量名 db 表达式1,2 用单引号括起来

?表达式:代表只分配空间

dup表达式:表示把括号内的内容重复n次 如:da_b1 db 10h dup(?)重复16次

常量:数值型二进制后b,八进制o,十进制d或不加,十六进制h 汇编语言不区分大小写 字符串常量:单引号括起来 常量可以作为立即数,位移量,初始值

变量:直接寻址:data_var +08h

标号: 在操作语句前 ,代表指令在代码段内的偏移地址,分为near: far:,默认近标号,如next:可以用label伪指令设置:sub1_far label far / sub1: mov ax,1234h 与数据定义配合使用:data_byte label byte / data_word dw 20h dup(563h)

运算符:

?地址是以字节为单元吗

数值返回运算符 <地址表达式>:seg返回段值 offset返回变量所在偏移 type返回类型 length元素个数 size所占字节数 size=l*s

Org 30h:预留30字节空白区域

Lea bx,var = mov bx,offset var

Length 如果变量用dup定义,返回外层dup,没有dup无论如何返回1

属性运算符:类型 ptr 地址表达式

Label ptr this都是给变量或标号另外的属性

段结构伪指令

Start: mov ax,data-dis

Mov dis,ax

Mov ax ,data-es

Mov es,ax

Ss装入 stack1 segment para stack

Dw 20h dup(?)

Stack1 ends

过程定义

过程名 proc[near/far]

Org 将表达式的值给位置计数器(汇编编译器的,用$表示,指令或分配空间都会增加)(每段开始清零,记录下一条数据或指令位置)

有条件跳转只能短跳(+-128字节),无条件可以长跳转

大小 正负 是否为0 cmp。判断某些位0/1做与运算用test

无符号数用JA JB JZ JE比较,有符号数JG JL

mov后面可以跟ascii码,也可以用单引号括字符

循环程序设计

1.初始化:设置地址指针、计数器初值

。。。

用计数控制循环:

Mov cx,次数

标号:[循环体]

Loop 标号;loop会自动将cx-1,直到cx=0

Mov count,次数/0

标号:[循环体]

Dec count/inc count

Jnz 标号;jnz:jum not zero/cmp count,次数 jnz 标号

条件控制循环:

初始化

标号l1:循环体

Cmp/test 退出条件

Jxx l1

嵌套循环:

Mov cx,外循环次数

L1:。。。。

Mov temp,cx/push cx

Mov cx,内次数

内循环

Loop l2

Mov cx,temp/pop cx

Loop l1

子程序设计

过程名 proc 类型:near/far

语句

一般不定义变量

过程名 endp

过程调用:

Call 过程名

过程返回:

Ret

返回地址从zhan中弹出到ip(cs)中

返回调用点

段内:ret

段间:ret n;同时弹出n个字节的数据

保护信息:

不建议在主程序实现

子程序中实现(用堆栈):

Sub_proc1 proc

Push bx

…

Pop bx

Rest

Sub_proc1 endp

参数传递:

通用寄存器R传递(适合参数较少的情况):

用公共变量传递:

用堆栈传递(高级语言编译器选用的方式):

DOS要求:1,2,9,0A号系统功能

1.MOV AH,1

INT 21H

5.LEA DX,字符串;要求以$结尾,不显示$

MOV AH,9

INT 21H

6.LEA DX,字符串缓冲区首地址

MOV AH,0AH

INT 21H

调试:设置断点、单步运行、运行到断点

第一章:1.1不用看 1.2.1和1.4

主机:cpu和主存

cpu:控制器和运算器

cpu的性能:cpu的字长、频率

总线的交换速度与宽带:外频粗略决定CPU与主存的数据交换频率

缓存对计算机系统性能的影响也很大

指令系统

第二章:要求掌握,重点浮点数,iee754

符号位S+阶码E(整数)+尾数M(1/2<=小数<1)

Iee754: 1数符+8阶码+23尾数

阶码的范围是1~254,实际表示-126-127

尾数隐含最高位=1,表示1.M

第三章:3.1.3不用看 3.1.2不用看 重点补码加减、溢出判断、位运算、浮点运算(加减乘除)、整数乘除

3.1.1 全加器通过两个操作数和一个低位传来的进位得到结果和进位

补码加法、减法,减法变负数补码,负数变补码:符号位不变,从右往左第一个1与以前的0不变,以后的高位取反

溢出 1.用符号位判断 2.用最高位和符号位的进位判断(如果最高有效位进位,符号位不进位,正溢) 3.变形补码(拓展符号位,第一位表示正负,第二位不同则溢出)

位运算 1.算数移位,不带符号位,正数都补0,负数原码补0,补码左移补0,右移补1,反码都补1

2.逻辑移位 全补0

3.循环移位

浮点运算

整数乘除

第四章:4.2.5 4.3.4 4.4.4不用看 重点掌握寻址方式 可变址操作码的扩展 地址格式分类、含义 cisc、risc特点 如何缩短指令字长度

可变长操作码:比如OP在最后四位之前都是1111

Complex instruction set computer:指令系统庞大,有多种字长和寻址方式

Reduced instruction set computer:较少的指令、寻址方式,字长固定,只有读数取数访问主存,简化硬件结构,减少指令执行的周期数

地址格式:各种地址的指令/访问主存或寄存器

寻址方式:隐含寻址、立即寻址、寄存器寻址、内存:直接寻址(直接访问内存)、间接寻址(从内存地址跳转)、寄存器间接寻址(寄存器存储内存地址)、变址寻址(寄存器存储地址与指令地址相加)、基址寻址、相对寻址(PC计数器+位移量)、堆栈寻址

第五章:不用看

第六章:6.2.6不看 6.4 6.5看第一小节 6.6不用看 重点6.1、6.2,各种存储器特征,刷新,扩展,会画扩展图,算根数 6.3大概知道 6.4 6.5知道cache概念

随机存取存储器 RandomAccessMemory

只读存储器 ReadOnlyMemory

顺序存取存储器 SequentialAccessMemory

直接存取存储器 DirectAccessMemory

刷新:集中刷新(刷新周期最后一些周期)、分散刷新(每次读取)、异步刷新(在刷新周期内把刷新平摊到一小段时间一次,刷新周期/行数)

扩展:位扩展,地址线连一起,cs、we连一起,d7-d0数据线独立;字扩展:地址(高位A12-A0)、数据、WE并联,高位A14、A15经过译码器产生4个CS信号

第七章:7.5以后不用看 7.1-7.4 cpu与外设的通讯方式 及过程 中断的概念及处理过程、优先级、嵌套、中断向量表、DMA和中断的比较

程序直接控制、程序中断、直接存储器存取(DMA交换文件)

主机响应外设请求暂时中断正在执行的程序,处理完外部事件后再返回原断点的过程称为中断

请求、判优、响应、处理、返回

从中断向量表取出中断程序入口,向量表存在000-3FFF

DMA不占CPU资源,每个机器周期都可以响应,优先级高于中断,DMA不能处理异常

第八章以后:汇编

[…] 未整理的计组复习笔记? […]